作者:張佑祥、梁烝輔、王偉彥、陳玠錡、黃萌祺

三維封裝與異質整合技術可利用中介層(Interposer)等相關技術,將不同功能的晶片模組整合在一起,使得晶片模組的效能更加強大[1]。所以中介層的製造、基板材料的特性與封裝結構的設計,成為中介層研發中不可忽略的關鍵因素。近年來,由於三維封裝和異質整合技術的需求,包含扇出型晶圓級封裝(Fan-out Wafer Level Packaging, FOWLP)與扇出型面板級封裝(Fan-out Panel Level Packaging, FOPLP)開始與日俱增[1],所以開發中介層技術也顯得越來越重要。但是傳統以矽為材料的中介層技術會遇到製造成本過高與封裝材料匹配性的問題等。然而,玻璃基板具有許多矽基板沒有的特性,例如:低介電係數、超高電阻率、高尺寸安定性、與銅的熱膨脹差異小以及良好的機械性質[2],甚至還可以彎曲應用在卷對卷(R2R)的製程上[3]。因此以玻璃作為基板材料的中介層也變成各大封裝廠商關注的熱門話題。

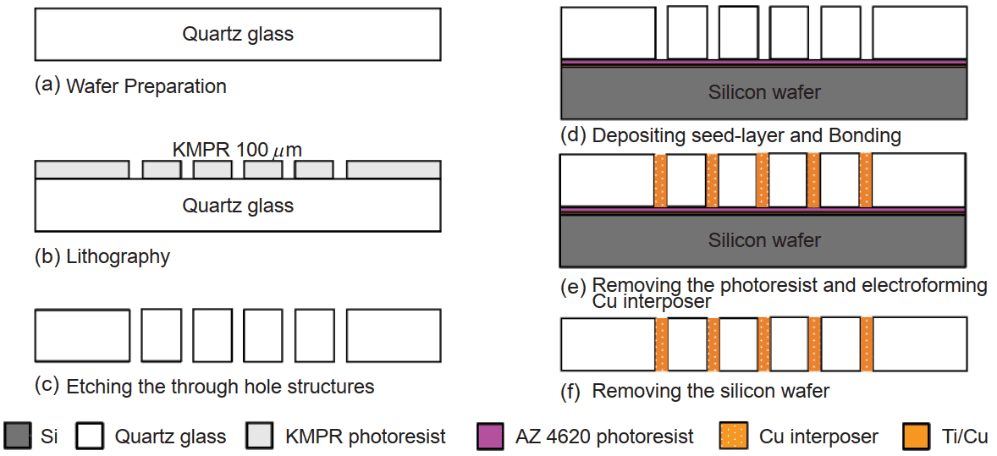

由中介層的結構應用上可知,中介層需要一個立體的金屬內接導線(Interconnect)作為上下訊號的通道,所以通常會在玻璃基板上加工,製造出具有一個高深寬比(High Aspect Ratio, HAR)的通孔(Through via)或盲孔(Blind via)的玻璃基板,即玻璃穿孔(Through Glass Via, TGV)基板。一般而言,玻璃穿孔可利用雷射鑽孔(Laser drilling)、超音波鑽孔(Ultrasonic drilling)、微放電加工(Micro Electrical Discharge Machining, μ-EDM)、微細磨料噴射加工(Micro powder blasting)或是感應耦合電漿離子蝕刻(Inductively Coupled Plasma Reactive Ion Etching, ICP-RIE)進行TGV的製作[4]。可是,當TGV被製作完成後,如何將TGV金屬化卻成了一個很大的難題。其原因乃因為一般中介層的厚度尺寸約略在100 μm ~ 400 μm,若TGV基板厚度較厚(400 μm),在製造的過程中可透過不同製程整合流程來達成,如圖1所示[5]。但若TGV基板的厚度較薄(100 μm),在製造中會遭遇因製程所造成的應力形變或破壞,使得玻璃基板產生缺陷或破裂。另外,TGV基板中其孔洞的深寬比通常較大(AR = 4 ~ 12)

圖1 玻璃通孔導線結構製程示意圖[5]