工研院資通所 林鴻宇 李威璁

隨著聯網裝置與數位服務的爆炸性成長產生了巨量的資料傳輸需求,如自駕車、機器人,皆需要大量的、低時間延遲的、不失真的高速傳輸需求,因此帶動了第五代行動通訊系統(5G)快速的成長,而以相位陣列技術組成之巨量天線(Massive multiple-input and multiple-output, Massive MIMO)即是達成上述需求的關鍵。但在毫米波段,5G巨量天線之相位陣列系統設計上將面臨兩個主要問題:

其一,為了增加波束集成天線的隔離度以及避免柵波瓣(grating lobe)問題,天線之間需要有一定的空間距離(如40 GHz需要 0.375 cm的距離,3.5 GHz 需要4.3 cm的距離)。在相同空間下選用越高的頻率,擺放的天線數量越多(以長寬皆為20cm的範圍為例:毫米波段40GHz可放約2900根天線;3.5 GHz可放約25根天線 ),連帶相同面積下主被動元件需求量劇增,在毫米波段下單一天線射頻單元容許之置放空間將極為狹小。

其二,儘管可以透過波束成形(Beamforming)將電磁波能量集中在特定方向,增加訊號發射強度,有效降低訊號在高頻傳輸損耗過大的影響(可讓訊號傳更遠),然而波束成形技術使用的天線數量與波束集成的角度成反比,在相同的傳輸距離之下(即相同的輸出功率),使用的天線越多則目標因為波束集成的角度越小而不容易被搜索,因此,必須提高功率放大器的線性功率來緩解此問題,使得相位陣列的天線數量可以被減少而增加波束集成的角度。綜合上述兩個議題,設計一個高線性功率、高效率及面積精簡符合第五代行動通訊系統的功率放大器是不可或缺的。

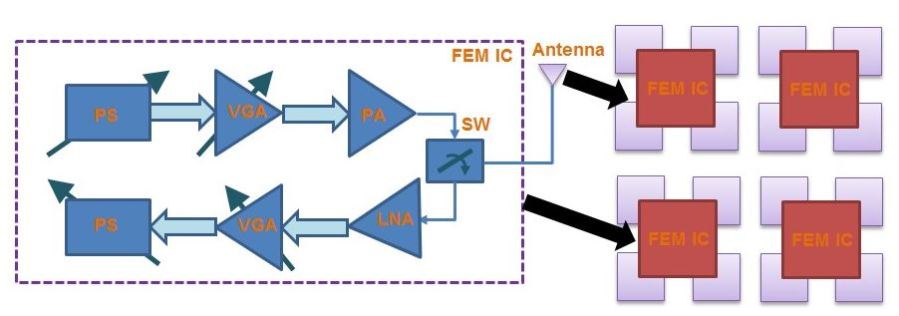

為設計能符合5G毫米波段之巨量相位陣列需求之功率放大器,其高線性功率、高整合度等特性是必要的。如圖1為 5G天線射頻單元之前端高整合度IC架構示意圖,包含功率放大器、低雜訊放大器、開關及相移器等元件。

圖1 天線單位元5G 高整合積體電路示意圖

線性化技術發展現況

為了使頻譜有效地被使用,使用較為複雜的數位調變機制是必要的。然而,複雜的數位調變機制伴隨著較高的波峰及平均值比(Peak to Average Power Ratio, PAPR),這會造成訊號經過高功率放大器後扭曲失真,使訊號不容易被解調。為了解決訊號失真問題,各種線性化技術如下:

- 自動偏壓調整式(Adaptive Bias)

將功率放大器操作在中低功率區來維持訊號的正確性,稱為功率退回(power back-off, PBO)。以文獻[1]-[2]為例,儘管它們有著傑出的最大輸出功率,但是功率退回後之最大效率與最大輸出功率下的效率有著很大的落差。自動偏壓調整式功率放大器可以改善功率退回後,功率放大器效率不佳的情況,其機制為低功率操作時將電路偏壓在AB類放大器,可以降低靜態電流並且降低功耗,當操作功率增加時,可以調整偏壓至A類放大器使功率放大器正常操作[3],因此,這個技術可以增加功率放大器的整體效率。 - 訊號前授(Feed-forward)

訊號前授的技術主要是將訊號分成主路徑及副路徑,主路徑為訊號主要操作的路徑,副路徑則是用來消除主路徑的非線性訊號,像是三階交互調變項來增加線性度。適當的調整副路徑的相位即可有效消除三階交互調變訊號以增加線性度。以文獻[4]為例,能有效消除三階交互調變失真藉由輸入反射訊號來當作副路徑的前授訊號。 - 預失真技術(Pre-distortion)

預失真技術能補償功率放大器之增益壓縮(gain compression)特性,使最大輸出功率提升進而提升效率及線性度[5]。然而,預失真線性化技術實現上較為複雜,容易受製程、偏壓以及溫度(PVT)變異的影響而使特性不如預期。同時因為需占用較大面積,運用在5G毫米波相位陣列中相對困難。 - 相位補償(受振幅調變)(Amplitude Margin to Phase Margin Compensation)

為了符合面積及高線性輸出功率需求,相位補償技術是一個有效增加線性輸出功率的方法。文獻[6]利用P-type電晶體相位增加的特性來補償N-type電晶體相位壓縮的問題,達到相位補償以增加線性輸出功率,此技術具低複雜度與占用面積小之優勢。因此,適用於高線性功率、高效率及面積精簡的5G功率放大器。

應用於砷化鎵製程之相位補償技術

採用砷化鎵(Gallium Arsenide, GaAs)製程優點為崩潰電壓高(高電壓擺幅)及基板損耗小,有利於高功率放大器的設計。然而砷化鎵製程僅有N-type的高電子遷移率電晶體,所以上述的線性化補償技術並不適合於此製程。有鑑於此,工研院資通所提出一個適用於砷化鎵製程的相位補償技術,可用於毫米波頻段的高功率放大器。

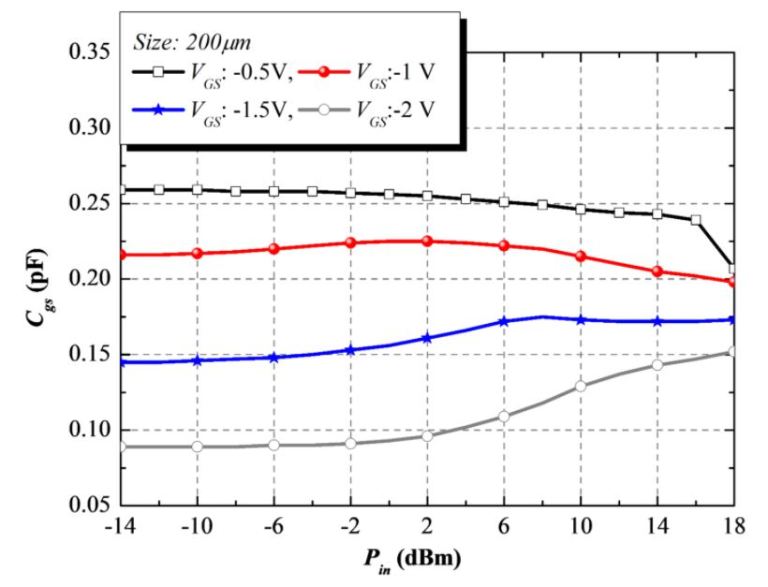

圖2 砷化鎵製程電晶體在偏壓(VGS)從-0.5 變化至-2V時,寄生電容Cgs 隨輸入功率的變化(電晶體尺寸為 μm)

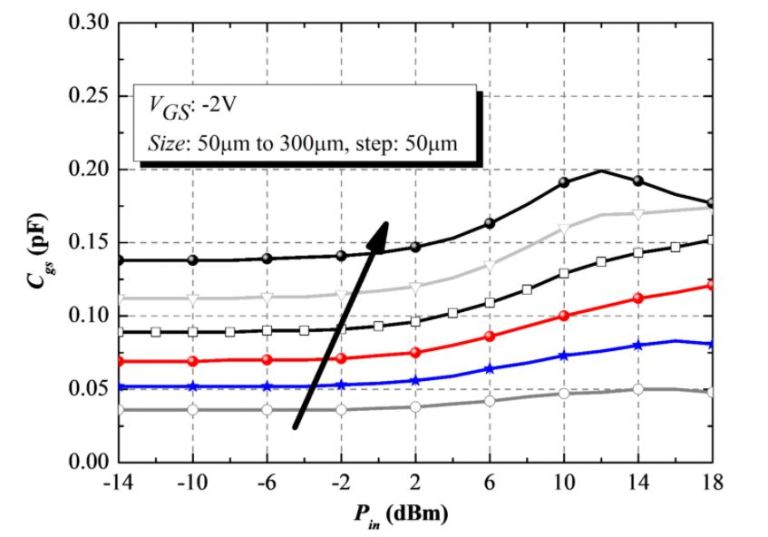

圖3 砷化鎵製程電晶體尺寸從 μm 變大至 μm時,寄生電容Cgs 隨輸入功率的變化

一般而言,相位失真源自於電晶體的閘極至源極的寄生電容Cgs,隨著功率放大器輸入訊號增加,會使寄生電容產生變化。當高頻訊號路徑上的電容產生變化,會使輸出訊號產生相位差異,進而導致輸入調變訊號時,輸出訊號的誤差向量幅度(Error Vector Magnitude, EVM)會隨之增加,造成解調訊號失真。為了緩解此問題,資通所團隊提出使用反向變化的電容元件來補償此寄生電容效應。圖 2模擬砷化鎵製程電晶體操作在截止區(VGS 偏壓< -1.5V)時,寄生電容Cgs隨輸入功率增加呈現反向的電容性變化,可用來補償操作在飽和區(VGS偏壓= -0.5V)的功率電晶體。又由圖 3可觀察到電晶體尺寸變化時,寄生電容Cgs之變化與電晶體尺寸大小呈正比。因此適當調整砷化鎵製程電晶體尺寸及工作偏壓,其相位差異可以被補償進而改善EVM。

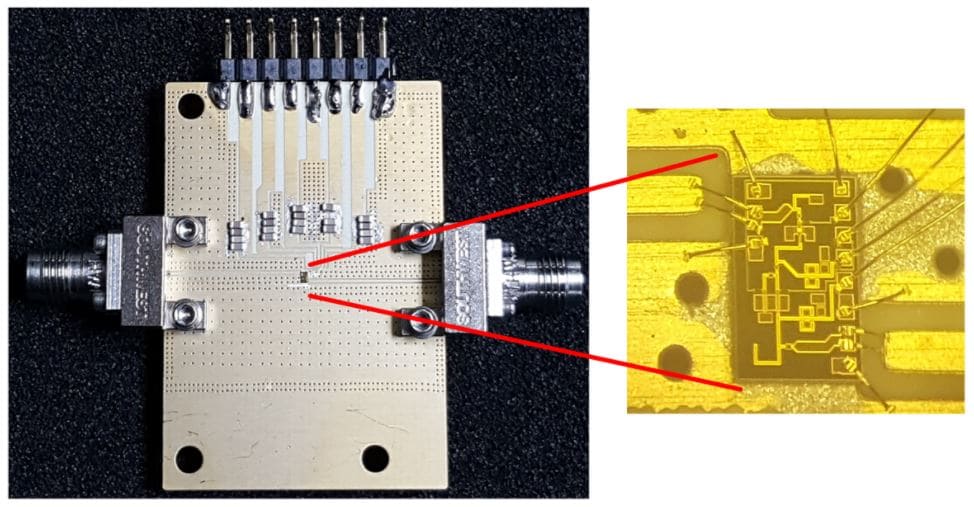

圖4 實現之砷化鎵晶片圖,大小為1.2 0.7 mm2

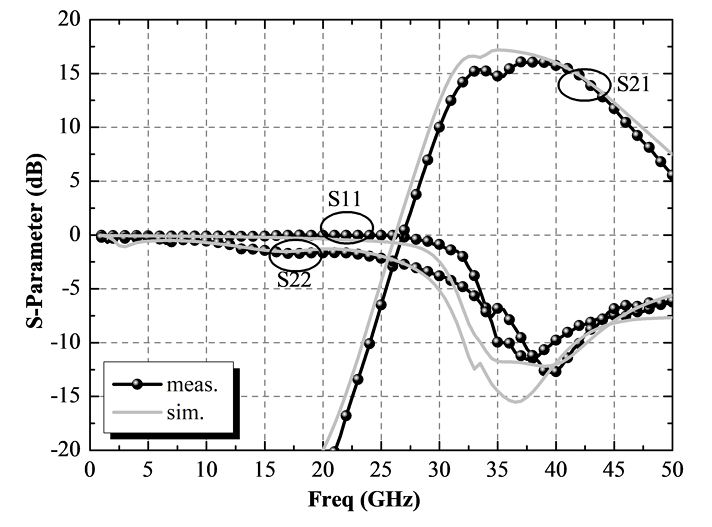

圖5 量測之小訊號參數

資通所團隊已成功製作一示範晶片如圖 4,面積為0.7×1.2mm2,其中包含所有的電路測試接點。圖 5為此晶片經電腦模擬與實際量測的小訊號參數比較圖,量測到的小訊號增益在40GHz頻率下為15.7dB。

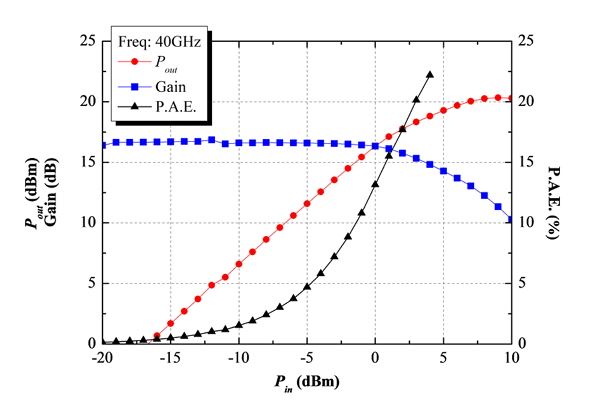

圖6 量測之大訊號功率特性

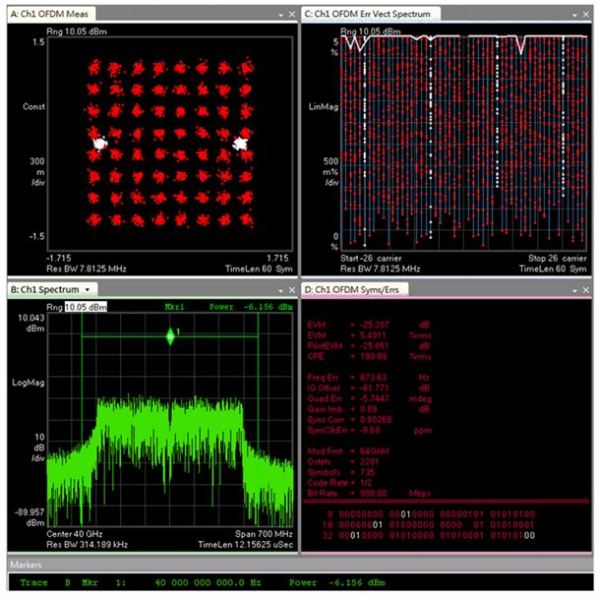

圖7 OFDM 64-QAM 500MHz 頻寬調變訊號測試

圖 6為此晶片之大訊號功率特性圖,量測到之OP1dB及PAE參數分別為17.5dBm及17%。圖 7顯示在OFDM 64-QAM500 MHz的調變訊號測試下,EVM小於-25dBc之高線性度測試條件下,此晶片具有13.7dBm的最大輸出功率及7.4%之功率轉換效率。

功率放大器載板隨5G時代來臨的發展

目前常見的PCB電路板主要使用聚醯亞胺(Polyimide, PI)材料包裹銅箔製成。為了更加輕薄化,電路板上傳輸資料的銅箔厚度12微米厚度逐漸壓縮成6~9微米的超薄壓延銅箔。高速傳輸中,超薄銅箔會產生高溫。由於聚醯亞胺(PI)材料的薄膜熱傳導係數和銅箔有差異。最終會導致PCB電路板基板翹曲,影響傳輸速度。而新型柔性電路板採用一種叫液晶高分子(Liquid Crystal Polymers, LCP)的液晶聚合物來製作,可以控制分子取向方向來調節熱膨脹係數,最終達到和銅箔接近的效能,從而避免因為高溫發生基板翹曲,來承受更加高速的傳輸速度。日本公司村田製作所和台灣公司嘉聯益對此材質投入多年的研發及生產研究,因此與蘋果一拍即合,蘋果之所以使用這種LCP天線,很明顯就是清楚未來5G網絡將會使用更高頻率的通信頻段(28GHz、38GHz),目前已有的材料不能完全滿足未來需求,而LCP 材料介質損耗與導體損耗更小,同時具備靈活性、密封性,因而具有很好的製造高頻器件應用前景。

總結而言,本文簡介5G毫米波功率放大器線性化技術之現況,並提出一種適用於砷化鎵製程的相位補償技術,可用於毫米波頻段的高線性度功率放大器。此線性化技術之優點為低損耗、零功耗以及面積精簡,且有效補償相位的差異以提升放大器的線性表現,適用於5G相位陣列兼具小面積(柵波瓣問題)及大功率(傳輸距離與波束集成的角度)的需求。實做之晶片可符合OFDM 64-QAM 500MHz調變訊號之高線性放大需求,搭配LCP FEM載板可滿足未來5G基站需求(單一通道頻寬大於250MHz)。

參考文獻

[1]C.F. Campbell, D.C. Dumka, M.Y. Kao, D.M. Fanning, “High Efficiency Ka-Band Power Amplifier MMIC Utilizing a High Voltage Dual Field Plate GaAs PHEMT Process,” in IEEE Comp. Semi. Integrated Circuit Symp. Dig. (CSICS), pp.1-4, Oct. 2011.

[2]K. Datta, J. Roderick, H. Hashemi, “A triple-stacked ClassE mm-wave SiGe HBT power amplifier,” in IEEE Int. Microw. Symp. Dig. (IMS), pp.1-3, June 2013.

[3]N.-C. Kuo, J.-C. Kao, C.-C. Kuo, and H. Wang, “K-band CMOS power amplifier with adaptive bias for enhancement in back-off efficiency,” in IEEE MTT-S Int. Microw. Symp. Dig., June 2011.

[4]N.-C. Kuo, J.-L. Kuo, and H. Wang, “Novel MMIC power amplifier linearization utilizing input reflected nonlinearity,” IEEE Trans. Micro. Theory Tech., vol. 60, no. 3, pp. 542-554, Mar. 2012.

[5]K.-Y. Kao, Y.-C. Hsu, K.-W. Chen, and K.-Y. Lin, “Phase-delay cold-FET pre-distortion linearizer for millimeter-wave CMOS power amplifiers,” IEEE Trans. Micro. Theory Tech., vol. 61, no. 12, pp. 4505-4519, Dec. 2013.

[6]C. Lu, Anh-Vu H. Pham, Michael Shaw, Christopher Saint, “Linearization of CMOS broadband power amplifiers through combined multigated transistors and capacitance compensation,” IEEE Trans. Microw. Theory Tech., vol. 55, no. 11, pp. 2320-2328, Nov. 2007.

[7]XB1017-QT 37.0-40.0 GHz Power Amplifier, MACOM Datasheet, http://www.MACOM.com.

[8]W.-T. Li, C.-C. Shen, and S.-M. Wang, “A 2.6 GHz RF Power Amplifier with 25.6 dBm Linear Power and -47 dBc ACLR for Small-cell Applications,” in IEEE Int. Microw. Symp. Dig. (IMS), pp.627-629, June 2017.

[9]S. Shakib, H.-C. Park, J. Dunworth, V. Aparin, and K. Entesari, “A highly efficient and linear power amplifier for 28-GHz 5G phased array radios in 28-nm CMOS,” IEEE J. Solid-State Circuits, vol. 51, no. 12, pp. 3020–3036, Dec. 2016.

[10]S. Kulkarni and P. Reynaert, “A push-pull mm-Wave power amplifier with <0.8゚ AM-PM distortion in 40 nm CMOS,” in IEEE Int. SolidState Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2014, pp. 252–253.